# THD COMPARISON @ SINGLE PHASE SINGLE STAGE THREE-FIVE LEVEL CONVERTER

**Haider Ahmed Mohmmed**

Assistant Lecturer, Faculty of Engineering, University of Kufa, Al-Najaf, Iraq

#### **Abstract:**

In this paper, the harmonic distortion rate for the single phase single stage three, five level AC-DC converter is presented. Multilevel converters are used in high voltage and high power applications of industry field, this converter achieves power factor correction, output voltage regulation in a single stage of power conversion, and lower total harmonic distortions by using multilevel diode clamped inverter. Increase the number of levels, the synthesized output wave form has more steps, producing a very fine stair case wave and approaching very closely to the desired sine wave and thereby the harmonics decrease, the waveforms are of high quality with a THD approaching zero. Total harmonic distortion must take into consideration for some applications such as uninterruptable power supply, motor drive systems, etc. Converter description, analysis and design considerations are explained.

### 1. Introduction:

A multilevel converters play a significant role in some applications in which a signal close to a sinusoidal waveform with low harmonic distortion should be generated. These converters are applied to high voltage and high power applications due to better harmonics and faithful output. A multilevel converters have been developed in recent years, these converter is typically done using a six switch front end ac-dc converter to do the power factor correction and a for switch full bridge converter to do the dc-dc conversion[1]. This approach, however, is expensive and complicated and to reduce the cost and increase the power density, The PFC circuit and the dc/dc power conversion circuit are combined into one stage in the single-stage PFC approach, sharing the same power switch and control circuit to perform input current shaping, electrical isolation, and tight output voltage regulation [2]. A multilevel converter have many advantages when compared to the conventional converter (two level) such as

- ✓ Reduced switching stresses on devices and since the dv/dt is low, the EMI from system is low.

- ✓ Low total harmonic distortion, lower switching frequency can be used and hence reduction in switching losses.

- ✓ Applicable for high voltage applications and produce higher voltage levels.

## 2. Converter Description:

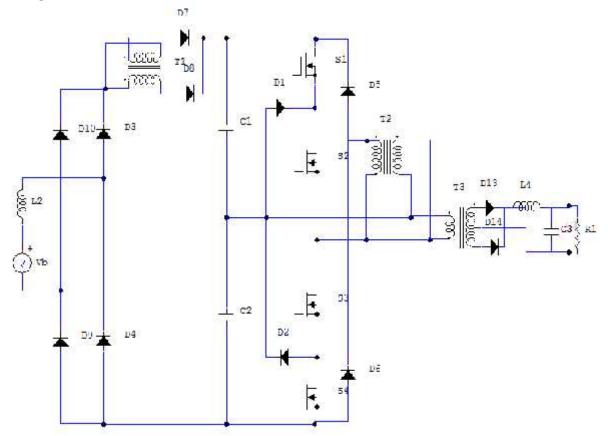

The structure of the single phase single stage three level full bridge converter shown in Figure 1. Consists of a three phase ac input section with an uncontrolled diode rectifier followed by the auxiliary windings taken from the converter main transformer. Then a multilevel type full bridge inverter is placed followed by the output transformer and the load. The basic principle behind the multilevel type full bridge converter is based on the combination of input inductors and auxiliary windings which carry out an action of PFC [3].

Initially the rectifier which consists of four diodes is supplied by a single phase voltage system. In each point two diodes of the diode bridge conduct resulting in an input current for discontinuous conduction mode (DCM) and continuous conduction mode (CCM) operation. The next section in the converter is the auxiliary windings that are taken from the converter main transformer which performs PFC by acting like a

boost switch with the input inductors by cancelling the dc bus capacitor voltage so that the voltage that appears across the diode bridge output is zero. This voltage cancellation occurs whenever there is voltage across the main transformer winding and current in the input inductors rises when it does.

Figure 1: Matlab/Simulink Model of Existing Single-Stage Three Level Converter

When there is no voltage across the main transformer primarywinding, the total voltage across the dc bus capacitorsappears at the output of the diode bridge; since this voltageis greater than the input voltage, the input currents falls. If the input currents are discontinuous, they will be naturally nearly sinusoidal (when filtered) and in phase with the inputvoltages.

Then the multilevel type full bridge inverter used for inversion. The diode clamped inverter delivers the staircase output voltage using several levels of DC voltages developed by DC capacitors. If m is the number of level, then the number of capacitors required on the DC bus are (m-1), the number of power electronic switches per phase are 2(m-1) and the number of diodes per phase are 2(m-2). Here the bus voltage is split among the capacitors equally, and the voltage stress across each switch is limited to one capacitor voltage through clamping diodes; thereby reducing voltage stress. By this design the flexibility of the converter is improved as shown in the figure 2. A diode clamped multilevel converter (DCMLI) is chosen because it have many advantages [3] such as:-

- ✓ When the number of levels is high enough, the harmonic content is low enough to avoid the need for filters.

- ✓ Inverter efficiency is high because all devices are switched at the fundamental frequency.

- ✓ The control method is simple.

ISSN (Online): 2455 - 4200

(www.rdmodernresearch.com) Volume I, Issue I, 2016

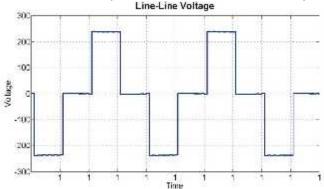

Figure 2: Line-Line Voltage

The switching sequences to generate the three-level output voltage are shown in table 1, As the number of levels increase the harmonic distortion decreases and efficiency of the inverter increases because of the reduced switching losses. The number of levels in multilevel inverters is limited because of the large number of clamping diodes required. And this sequence can be extended to any number of levels of inverter [3].

Table 1: Switching sequence for three level inverter

|               | Output voltage |      |        |

|---------------|----------------|------|--------|

| Switch number | +Vdc/2         | Zero | -Vdc/2 |

| Switch 1      | 1              | 0    | 0      |

| Switch 2      | 1              | 1    | 0      |

| Switch 3      | 0              | 1    | 1      |

| Switch 4      | 0              | 0    | 1      |

The steps to synthesize the three level voltages are as follows:

- a. For an output voltage level Vao= Vdc/2, turn on all upper- half switches S1 through S2 as shown in figure 3.2 (a).

- b. For an output voltage level Vao= 0, turn on one upper switches S2 and one lower switch S3.

- c. For an output voltage level Vao= Vdc/2, turn on all lower- half switches S3 through S4.

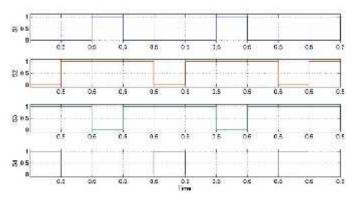

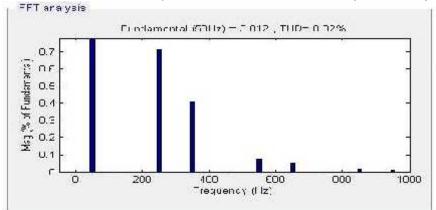

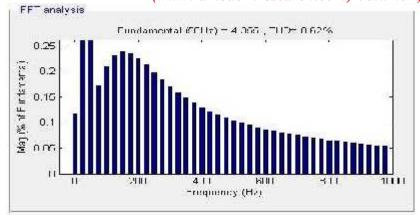

We used the Pulse Generator directly to generate the pulses, the pulse generator block generates square wave pulses at regular intervals. The block waveform parameters, Amplitude, Pulse Width, Period, and Phase delay, determine the shape of the output waveform as shown in the figure 3. And the total harmonic distortion THD (to the input filtered current) rate of the single phase single stage three level converter is as shown in the figure 4.

Figure 3: Pulse Generator

Figure 4: THD rate of single phase single stage three level converter

Various techniques for capacitor voltage balancing to ensure the voltage across each bus capacitor is the same, have been proposed in the literature, including techniques that sense the capacitor voltages and adjust the duty cycle of the converter switches appropriately. For this work, anadditional transformer with a turns ratio of 1:1 and two fast recovery diodes are required to realize the technique [5], which are used to assure equal voltage across the capacitors. This circuit is very simple, small, and handles only a small fraction of the overall power that is processed by the converter so that the low current rated diodes can be used (<1A) and a small core can be used for the transformer. The basic principle behind the auxiliary circuit is that if the voltage across one capacitor begins to be greater than the other by more than a diode drop, then one of the diodes begins to conduct as energy is transferred away from the capacitor with the higher voltage. Since the auxiliary circuit does not allow for large differences in bus capacitor voltage, the amount of energy that needs to be transferred away at any given time is small. When the auxiliary circuit is added to the main circuit, It forces a diode to conduct thereby dissipating energy, when a difference in voltage is noted. By this means capacitor voltages are being balanced.

# 3. Analysis of Multilevel DCMLI:

A multilevel structure with more than three levels can significantly reduce the harmonic content. By using voltage clamping techniques, the system KV rating can be extended beyond the limits of an individual device. The main feature of the multilevel inverter structures is their ability to scale up the kilovolt-ampere rating and also to improve the harmonic performance greatly without having to resort to PWM techniques [4]. The key features of a multilevel structures as follow:

- ✓ The output voltage and power increase with number of levels, adding a voltage level involves adding a main switching device to each phase.

- ✓ The harmonic content decreases as the number of levels increases and filtering requirements are reduced.

- ✓ With additional voltage levels, the voltage waveform has more free-switching angels, which can be preselected for harmonic elimination.

- ✓ In the absence of any PWM techniques, the switching losses can be avoided. Increasing output voltage and power does not require an increase in rating of individual device.

- ✓ Static and dynamic voltage sharing among the switching devices is built into the structure through either clamping diodes or capacitors.

- ✓ The switching devices do not encounter any voltage-sharing problems. For this reason, multilevel inverters can easily be applied for high-power applications such as large motor drives and utility supplies.

- ✓ The fundamental output voltage of the inverter is set by the dc bus voltage, which can be controlled through a variable dc link.

The only disadvantage of the multilevel converter is that it required a huge amount of semiconductors switches. It should be pointed out that lower voltage rated switches can be used in the multilevel converter and as a result the active semiconductor cost is not considerably increased when compared with the two level cases. On the other hand, each active semiconductor added requires associated gate drive circuitry and adds further complication to the converter mechanical layout. Another disadvantage which is to be mention is thatthe small voltage steps are typically formed by isolatedvoltage sources or a bank of series capacitors. Isolated voltage sources may not always be readily available and series capacitors require voltage balance. To some extent, the voltage balancing can be addressed by using an uncalled for switching states, which exist due to the high number of semiconductor devices. Nevertheless, for a complete solution to the voltage-balancing problem, another multilevel converter maybe is required.

# 4. Matlab/Simulink Mode Link and Simulation Results:

Single phase single stage three-thirteen level converter is simulated in MatLab/Simulink Software. A single phase source with terms voltage of 208 is connected with the input inductor (Lin) 60  $\mu\text{H}$ , this value of Lin should be low to assure input current to be fully discontinuous but not very low value leading to high peak currents. Then the auxiliary windings are taken from the multi winding transformer block in MatLab. They are connected in an indirectly coupled fashion. The other end of the winding is connected to the full bridge converter of multilevel type.

This converter consisting of 2(m-1) MOSFET switches (m is the number of levels) which are connected in a diode clamped inverter with 2(m-2) diodes and (m-1) capacitors. Next is the main transformer whose turn's ratio is 3:1. The voltage is rectified using the transformer and then is filtered using an LC filter .The value of output inductor (Lo) is designed such that it results in a low ripple at output and low peak current rating for secondary diodes. The value of Lo chosen is 11  $\mu H$ . This converter was designed according to the following specifications:-

Input voltage Vin= 208 Vrms (line-line)

Output voltage Vo= 48 v

Output power Po= 1.5 Kw

Switching frequency  $f_{sw}$ = 50 KHz

In the proposed converters all the above parameters are fixed, the only change in the full bridge multilevel inverter by increasing the number of switches, diodes, capacitors. This converter is simple (topology and capacitor voltage balancing), and can operate with less output inductor current ripple, operate with no dead band regions, the switch stress is half the dc bus voltage. The proposed converter has low THD, which is better than the converters in [6]-[8].

A comparative study of three, five, seven, nine, eleven, thirteen level diode clamped inverter has been presented in the table 2. Simulation results indicated reduction in total harmonics distortion (THD) by using higher number oflevels are shown in figures 2 to 7.

Figure 5: THD rate of single phase single stage five level converter

# **5. Comparison of Different Topologies Between Different Levels:**

A comparative study of three, five, seven, nine, eleven, thirteen level diodeclamped inverter has been presented in the table 4.1, Simulation results indicated reduction in total harmonics distortion (THD) by using higher number of level.

Table 2: Comparison of Different Topologies between Different Levels

| Topology      | Number of Levels |         |  |

|---------------|------------------|---------|--|

|               | 3 Level          | 5 Level |  |

| Current THD % | 0.82             | 0.62    |  |

## 6. Conclusion:

Usage of power electronic converters are ever increasing in the processing of electrical energy in industrial applications in which a signal close to a sinusoidal waveform with low harmonic distortion should be generated such as uninterruptable power supply, adjustable speed drives, switch mode power supply, etc. The comparative THD analysis of a single phase single stage three – five level ac to dc converter is performed. Converter is simple in capacitor voltage balancing and can operate with less output inductor current ripple, even continuous output inductor current. It is operated with lower peak voltage stresses across the switches and the dc bus capacitors as it is a multilevel converter. This allows for greater flexibility in the design of the converter and ultimately improved performance. From the above analysis, it is absorbed that the five level converter has less harmonic content with THD of only 0.62% in the input filtered current compared with the three levels by using MATLAB/SIMULINK.

#### 7. References:

- 1. P. D. Ziogas, Y. Kang, and V. R. Stefanovic, "PWM control techniques for rectifier filter minimization," IEEE Trans.Ind. Appl., vol. IA-21, no. 5, pp. 1206–1214, Sep. 1985.

- 2. J. Contreas and I. Barbi, "A three-phase high power factor PWM ZVS power supply with a single power stage," in IEEE PESC Conf. Rec., 1994, pp. 356–362.

- 3. Anssari, OthmanM. Hussein, and P. Satish Kumar. "Three phase single stage three-thirteen level ac-dc converter." IJEEER. Vol. 5, Issue 2, Apr 2015, 61-72 © TJPRC Pvt. Ltd.

- 4. Muhammad H. Rashid 'power electronics circuits, devices, and applications', third edition. Eleventh impression, 2011.

- 5. Y. Hung, F. Shyu, C. Lin, and Y. Lai, "New voltage balance technique for capacitors of symmetrical half-bridge converter with current mode control," in Proc. 5th Int. Conf. PEDS, 2003, pp. 365–369.

# International Journal of Engineering Research and Modern Education (IJERME) ISSN (Online): 2455 - 4200

(www.rdmodernresearch.com) Volume I, Issue I, 2016

- 6. Mehdi Narimani, Student Member, IEEE, and Gerry Moschopoulos, Senior Member, IEEE"A Novel Single-Stage Multilevel Type full-bridge converter" IEEE transactions on industrial electronics, no1, jan 2013.

- 7. F. Cannales, P. Barbosa, C. Aguilar, and F. C. Lee, "A quasi-integrated ac/dc three-phase dual-bridge converter," in IEEE PESC Conf. Rec., 2001, pp. 1893–1898.

- 8. P. M. Barbosa, J. M. Burdio, and F. C. Lee, "A three-level converter and its application to power factor correction," IEEE Trans. Power Electron., vol. 20, no. 6, pp. 1319–1327, Nov. 2005.